УДК 621.396.61

Разработка моделей функциональных узлов выходной ступени тракта передачи

Разработка моделей функциональных узлов выходной ступени тракта передачи - так называется следующий четвертый раздела нашего проекта.

4.1 Постановка задач к разделу 4

В настоящее время существует большое множество различных методик расчета мощных высокочастотных каскадов радиопередатчиков [1…4]. Но все они в основном базируются на методе гармонической линеаризации и косинусоидальной зависимости напряжения на выводах МДП-транзистора.

Однако построение тракта усиления, имеющего максимальный коэффициент полезного действия, предполагает работу каскадов усилителя в ключевом режиме. При этом форма колебаний на стоках транзисторов становится далеко не косинусоидальной. В этих условиях применение классического метода анализа работы каскада становится не приемлемым, т.к. необходимо учитывать нелинейные явления, происходящие в самом транзисторе и схеме.

Методика анализа каскада при работе в этих условиях рассмотрена

в [5].

Однако методика [5] ориентирована на применение специализированной программы и достаточно сложна для применения специалисту, не владеющему специфическими знаниями программирования.

Наиболее приемлемым методом решения поставленной задачи является моделирование работы каскада с использованием существующих и широко используемых пакетов программ моделирования DESIGNLAB, ORCAD, PCAD2002, P-SPICE и др. [6].

Целью данной главы является разработка моделей функциональных узлов выходного каскада РПДУ, состоящего из усилителя и фильтра гармоник с использованием программы моделирования

Micro-CAP 9.

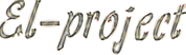

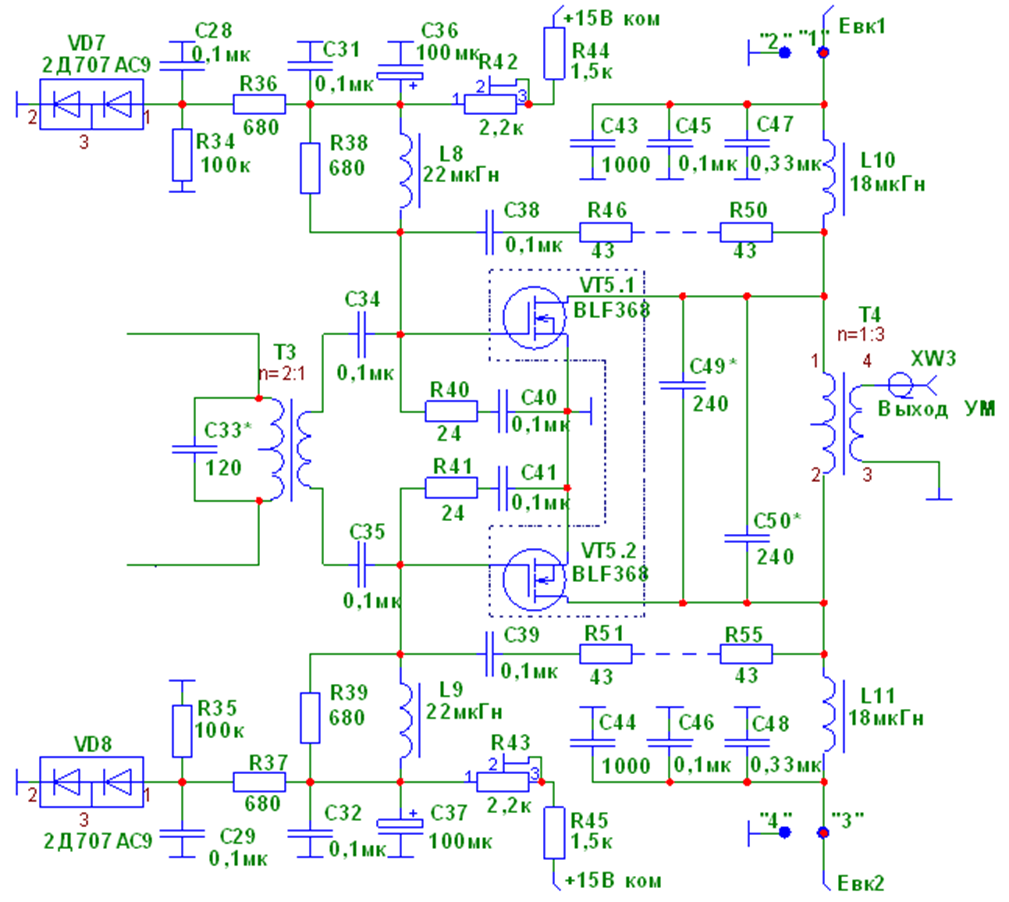

Схемы электрические принципиальные составных частей оконечной ступени РПДУ заданы заказчиком проекта и приведены на рисунках 4.1 и 4.2.

Примечание - Для того чтобы увидеть схемы в увеличенном размере произведите клик по их изображению, изображения при этом откроются в отдельном окне.

Рисунок 4.1 - Схема электрическая принципиальная усилителя мощности

Рисунок 4.2 - Схема электрическая принципиальная фильтра гармоник

4.2 Определение функциональных узлов, подлежащих моделированию

Техническим заданием задано моделирование выходного каскада передатчика, который совместно с фильтром гармоник определяет все выходные параметры тракта передачи РПДУ.

Рассмотрение схем электрических принципиальных рисунок 4.1, 4.2 показывает, что подлежащий моделированию выходной каскад передатчика состоит из следующих функциональных узлов:

- выходного каскада передатчика;

- фильтра гармоник (рисунок 4.2).

Схема электрическая принципиальная выходного каскада может быть получена из схемы рисунок 4.1 путем исключения второстепенных устройств, не определяющих основные его параметры, и приведена на рисунке 4.3.

Для моделирования выходного каскада передатчика необходимо создать модели следующих его функциональных элементов:

- модель транзисторной сборки BLF368;

- модель входного согласующего трансформатора Т3;

- модель выходного согласующего трансформатора Т4;

- модель источника двухчастотного испытательного сигнала;

- модель фильтра гармоник;

- модель комплексных нагрузок в заданном круге КСВ.

Рисунок 4.3 – Схема электрическая принципиальная

выходного каскада передатчика

4.3 Разработка модели транзистора выходного каскада

В выходном каскаде оконечной ступени тракта передачи используется сдвоенный транзистор типа BLF368 (Philips Semiconductors).

Поэтому до начала моделирования необходимо создать его модель.

Для многих транзисторов фирмы-изготовители обеспечивают потребителей P-Spice моделями. Такая модель для транзистора BFR368 создана изготовителем, однако она не доступна в открытых источниках информации. Поэтому сами создадим модель транзистора по его имеющимся справочным данным [7, 8].

Программа моделирования Micro-Cap 9 обеспечивает поддержку Spice моделей, BSIM моделей, EKV моделей и Philips MOSFET моделей различного уровня. Оптимальной моделью, для случая ее создания по справочным данным, является модель уровня 3 (MOS3 empirical model –

SPICE 3F5) [7, 8].

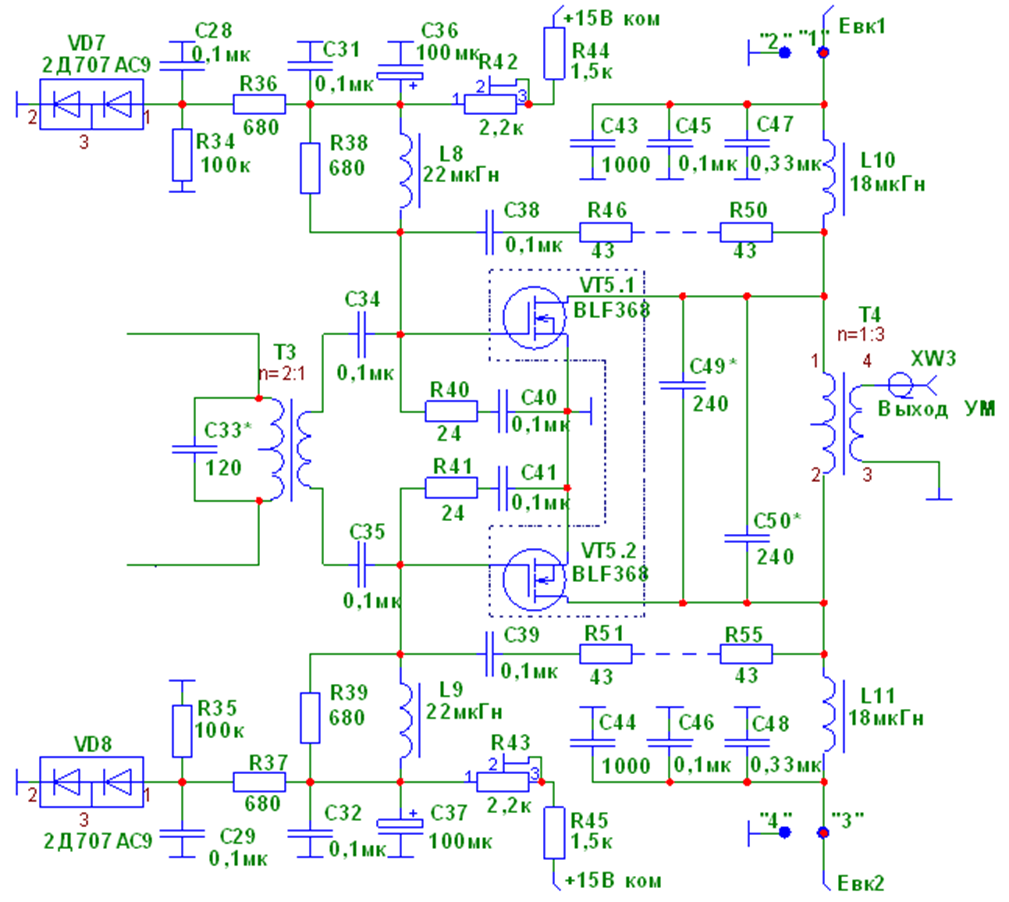

На рисунке 4.4 приведена эквивалентная схема нелинейной модели MOS-транзистора для уровней 1, 2 и 3 [7, 8].

Рисунок 4.4 – Эквивалентная схема модели MOS-транзистора

На рисунке 4.4 приняты следующие обозначения элементов модели MOS-транзистора:

GATE – вывод затвора транзистора;

CGD – емкость затвор-сток;

CGB – емкость затвор –подложка;

CGS – емкость затвор-исток;

DRAIN – вывод стока транзистора;

ID – зависимый источник тока стока;

RS – объемное сопротивление истока;

SOURSE – вывод истока транзистора;

DBD – паразитный p-n переход сток-подложка;

CBD - емкость p-n перехода сток-подложка при нулевом смещении;

CBS – емкость p-n перехода исток-подложка при нулевом смещении;

DBS – паразитный p-n переход исток-подложка;

RB – объемное сопротивление подложки;

BULK – подложка транзистора.

Для определения параметров эквивалентной схемы модели MOS-транзистора применяется программа расчета MODEL [7, 8], которая работает в интерактивном режиме и выполняет расчет и оптимизацию параметров модели по исходным паспортным данным, введенным в табличной или графической форме и взятым из информационных источников на моделируемый транзистор. Оптимизация выполняется с помощью прямого метода Пауэлла (метод оптимизации, известный в отечественной литературе, как метод наискорейшего спуска).

В качестве исходных данных для формирования модели транзистора BLF368 используем информацию, приведенную в pdf-файле [7].

Разработанная по методике [8] модель транзистора BLF368 представлена в таблице 4.1 в виде текстового файла в формате SPICE.

Для проверки адекватности созданной модели транзистора проведено моделирование ее S-параметров с целью сравнения полученных результатов со справочными данными S-параметров, полученными из [9].

Таблица 4.1

SPICE модель транзистора BLF368

.MODEL BLF368_PIM NMOS (LEVEL=3 CBD=1.92093727123N CGDO=47.752626819716P

+ CGSO=491.607149523244P GAMMA=0 KAPPA=0.2 KP=770U L=20U

+ LAMBDA=153.927828169557M NLEV=2 NSUB=0 PHI=600M RD=300.593375416591M RDS=6.4K

+ RG=90M RS=40M TOX=0 TPG=1 UO=600 VTO=2.999999999989 W=55.05989403731M)

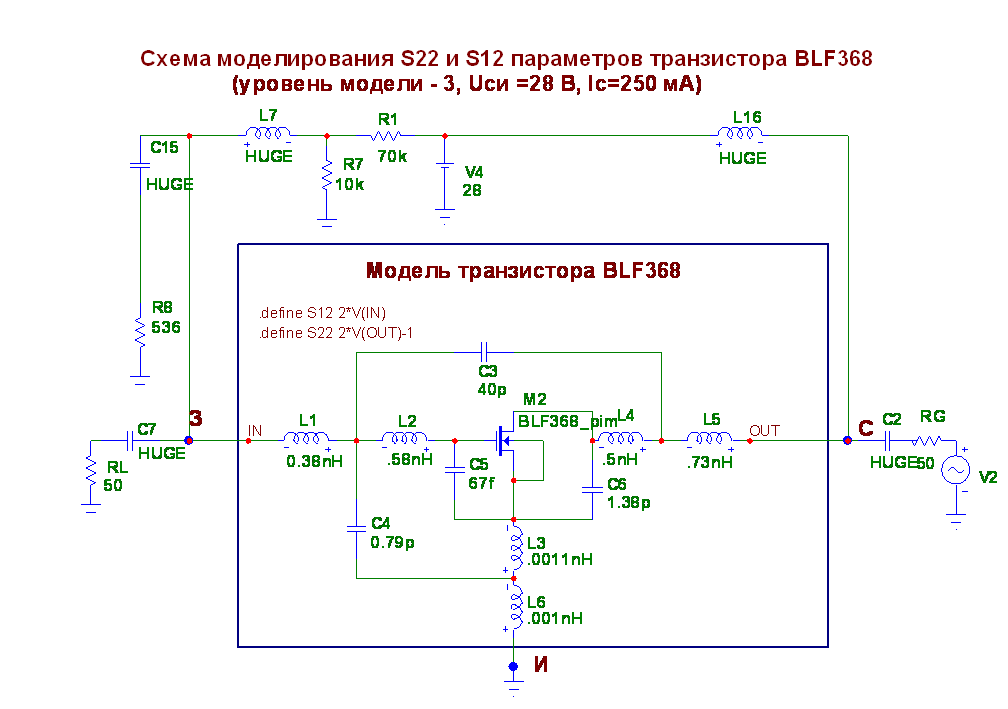

Проверку адекватности полученной модели проводим с помощью схем определения S-параметров в программе Micro-Cap 9.

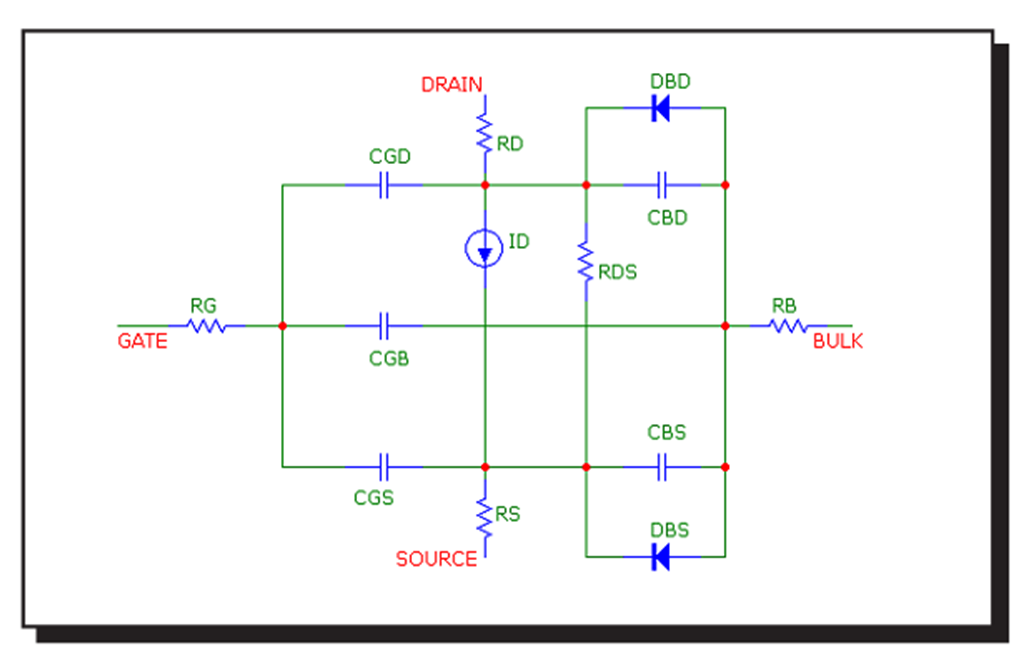

Схемы моделей для определения S-параметров транзистора BLF368 приведены на рисунках 4.5, 4.6.

Рисунок 4.5 – Схема моделирования S11 и S21 параметров

транзистора BLF368

Рисунок 4.6 - Схема моделирования S22 и S12 параметров

транзистора BLF368

Дополнительные элементы, входящие в схему модели транзистора, введены для учета паразитных индуктивностей выводов и паразитных межэлектродных емкостей транзистора. Значение этих элементов выбрано равным соответствующим значениям транзистора с идентичным по конструкции корпусом [10].

Полученные результаты моделирования S-параметров и данные S-параметров, взятые из [9] для сравнения и оценки точности созданной модели транзистора, приведены в таблицах 4.2, 4.3.

Таблица 4.2

Таблица 4.3

Анализ данных, приведенных в таблицах 4.2, 4.3, показывает достаточно высокую точность разработанной модели транзистора BLF368 и возможность использования ее при моделирования схем с применением данного транзистора.

Выводы

В статье начато рассмотрение следующего раздела проекта "Разработка моделей функциональных узлов выходной ступени тракта передачи.

Выполнена постановка задач раздела, приведено описание разработки модели транзистора BLF368 выходного каскада и выполнена проверка адекватности S-параметров разработанной модели

аналогичным параметров [9], приводимым в информационных материалах.

Анализ полученных результатов, показывает достаточно высокую точность разработанной модели транзистора BLF368 и возможность использования ее при моделирования схем с применением данного транзистора в диапазоне до 30 МГц.

СПИСОК ЛИТЕРАТУРЫ

- Проектирование радиопередающих устройств с применением ЭВМ / Под ред. О.В. Алексеева. – М.: Радио и связь, 1987. – 392 с. (3)

- Широкополосные радиопередающие устройства / Алексеев О.В., Головков А.А., Полевой В.В., Соловьев А.А.; Под ред. О.В. Алексеева. - М.: Связь, 1978. – 304 с. (4)

- Проектирование радиопередатчиков / В.В. Шахгильдян, М.С. Шумилин, В.Б. Козырев и др.; Под ред. В.В. Шахгильдяна. – М.: Радио и связь, 2000. – 656 с. (5)

- Каганов В.И. Радиопередающие устройства. – М.: ИРПО: Издательский центр «Академия», 2002. – 288 с. (6)

- Каганов В.И. Проектирование транзисторных радиопередатчиков с применением ЭВМ. – М., Радио и связь, 1988 (43)

- Амелина М.А., Амелин С.А. Программа схемотехнического моделирования Micro-CAP 8. М., Горячая линия-Телеком, 2007, 464 с. (24)

- «VHF push-pull power MOS transistor BLF368». Product specification Supersedes date of September 1992, Philips Semiconductors, 1998,

Jul 29, p.16. (37)

- Micro-CAP 9. Electronic Circuit Analysis Program Reference Manual. Spectrum Software, 2007. (44)

- Filename: BLF368_28v_250.s2p/ Philips part #:BLF368. !date:21-05-2003. (45)

- PSPICE MODEL FOR NINE RF N-CHANEL VERTICAL DMOS POWER FET, May 2004/www.point9.com, www.rfmosfet.com. (46)

|